https://www.t-firefly.com/themes/t-firefly/public/assets/images/coreboard/rk3399/part_2.png

第一课

1、不显示位号

第二课

1、对于 1.8V 以下的小电压,反馈点要从远处拉过来。

因为小电压,压降比较明显,到达芯片可能就不是 1V 了,变成 0.9V 了。下面是芯片 Demo 中的示意图,让从使用处拉过来反馈线。

第三课

1、两个 DDR 不要放的太近,不然后面走线困难。

一般来说,T 形(星形)走线比 Fly-By(菊花链)难。

第四课

1、它这个网络的飞线的显示开关是通过手势命令的

2、看 BGA 的电源在哪一部分,就近放置LDO、DC-DC电路

3、芯片上有散热风扇的话,要考虑在风扇下面,其它元件的高度不能超过主芯片

4、

16:30

第十课

1、基本布局后就可以开始走线了,因为走线的会时时调整布局,一开始是没办法得到一个完美的布局的,所以不必花费过多时间,应该后面还要改,那这个多余的布局纯纯浪费时间了。

2、一般先布DDR部分

3、DDR 地址线、数据线等共用的,就是一个通道。

4、一个通道的两个DDR使用T形拓扑,T形分为两种:

过孔对齐:难度相对大一点,一般是公司要求这样。例如:

过孔不对齐:比对齐难度小一点,一般自己画板子用这个,简单一点。

5、蓝色的是主要走线的,间距要大一点;黄色的间距可以小一点

这 4 片 Y 轴要一致,因为要按过孔对齐画。

左边两个和右边两个的间距(蓝色的那个间距)也要一样,这样后面可以直接复制走线过去。

先计算,然后移动时使用x命令移动到指定位置。

视频中的间距为 570 mil

这种多、小间距,而且离芯片很近,6层板几乎画不出来。

6、DDR 芯片 VREF 电容放在中间位置

7、BGA 焊盘间距和使用的过孔大小:

8、21:20 -----什么能不用就不用的

9、Allegro扇出方向

对于水平的,选择:BGA Quadant Style

对于45度的:选择 Outward

第十一课

1、设置原点,移动到元器件中心的话,输入元器件的坐标就行了。

2、大小栅格

3、26:20 什么9、10线尽量是直的,不要往外太多

4、电源过孔一般都是在4个脚移动,一般不会拉太远

5、实在拉不出来的话就不要考虑这个的过孔对齐了,但是要给它的走线留个位置。

6、ZQ电阻越近越好,如果实在要放远一点的话,要加粗走线,降低阻抗

7、拷贝扇出

对于相同的元件,选择哪个都可以:

这节课乱七八糟的,听不太懂。

第十二课

1、要取两个DDR的绝对中心位置,

2、T形拓扑过孔对齐,要 3 处过孔一致

中间的过孔,每6个或8个空一个过孔,太密集不好走线。

我觉得还是,一片连接到中间了,然后再复制,因为过孔可能调整。

3、DDR连接中间的走线,想办法使劲挤,不要浪费里面的空间。

4、时钟打在中间

第十三课

讲的是 pin delay,参考第 68 课。

那个从原厂的excel文件中复制那一列长度,直接复制不行,得:

取小数点后2位精度就可以了,单位转换:

如果 pin delay 功能未开启:

【setup】【constraints】【Mode】

Z Axis Delay:计算过孔的延时,不建议开。我们同组同层的走线,这个影响不大。

有两个,一个是CPU芯片的,一个是DDR的,DDR一般内部都是等长的,不用管。

这是按照一定的规则分配在 pin1或pin2,不管在前面还是后面都无所谓,不用纠结这个,一样的。

第十四课

1、T 先拉通地址线,因为比较麻烦。先走时钟线

2、中间的这一排,要保证有两层可以走线,顶层和内6层。

4、中间的和两边的ddr连接后,就要放置电容了。

地址线不用同组同层

5、这个可以统一改的:

6、出现小方框,把扇出关掉就行了。01:04:30

7、时钟线,要距离其它信号线远一点

个人感悟:

看这种 PCB 视频,完全跟上是不可能的,不可能说他画一下你跟着画一下,那一套课估计要看一年。

每个人的思维是不同的,只能说是学习他走线时解决问题的方法、一些经验,然后应用到你自己走线中。

第十五课

无。

十四课没讲完的。

第十六课

1、T形左右两边还没有做等长,等数据总线拉通后再做。

2、拉线时建议给网络组的管脚赋予颜色,方便走线时区分。

3、数据线用第 3 层和顶层,因为数据线需要同组同层,但是里面有几根线从第 6 层无法走出来。

4、bga后面的电容可以压在通孔的焊盘上,但是不要压在钻孔上。

5、3个以上相同网络的过孔,比如GND,可以删除一个。

6、DDR 的电源要预留空间,不然后期不好走线。它的参考电源、还有那个DDRPLL啥的电源,好像是CPU的引脚,因为只有一两个引脚,所以只能走线,而不能在电源平面铺铜,因为它会分割其他连续的电源铜皮。

妈的。调了一节课的电容。

第十七课

左边的 DDR 使用顶层+底层、右边的DDR使用顶层和第3层

第十八课

这节课讲的是最左边那个DDR的拉数据线,已看完。

1、T形拓扑,标准做法:A中的线和B中的所有线等长,就是A和B中所有线的长度一样,然后C的所有线的长度一样。

第十九课

这节课讲的是左边两DDR的等长(1)

1、设置 T 点

点击焊盘选择网络,然后右键【Insert T】

在中间位置空白处点击一下:

然后点击另一个管脚:

现在是在右边,要回到中间,因此再点击一下中间:

点击SOC上的引脚,最后再 Done 完成。

这个T点是飞线,把飞线打开就能看见T点了。

设置大小:

===========================

这是完成了一个,用这个批量生成:

14分的时候根据RK的手册得出长度误差,没看懂。

左右两端的 Rule Name 可以是一样的:

T-FROM_CPU_TO_T-POINT

T-FROM_T-POINT_TO_DDR

点击OK,然后:

弹出一个界面,点击确认,然后就可以关闭这个页面了。

关闭后会弹出,点击Yes:

最终会生成两个等长组,和一个规则:

此时给DDR地址组设置 CSet

它就会把所有等长组建立好:

如果说中间的没有连接在CPU上,那必须把 T 点手动放在中间的过孔上,此时Allegro计算的是到T点的长度,而不是到过孔的长度。

但是如果中间的连接在CPU上了,T点无论位置放哪,其实是没有影响的。

2、移动的时候捕捉到过孔上:

3、等长最难做的是中间的,因为线比较短,而且没啥空间。

4、如果线短,先在顶层尽可能拉到最长,减小内层的走线压力,然后再内层。

5、中间实在没地方了,没办法了,就2倍间距。很多时候只能手动拉蛇形

6、时钟线距离其它线最好是4W以上,最小3W

没啥技巧,调整线的时候,中间的留点空间。

这个T点有点毛病,就是某个网络连接好线后,他就不显示T点的飞线了,T点上也没有网络名,不知道哪个是哪个。

还好移动的时候,下面显示网络名称:

删除T点:

1、把地址线分配的分组,右键Clear清除

2、然后删除最初的那个T点

【Logic】【Net scheclude】

右键选择

然后点击那个T点就行了

3、规则管理器中创建的那个规则还在,给他删了。这里面删了,好像其他地方这个分组也删了。

T点的颜色指示器,使用规则管理器中的Select是没有用的,只能手动框选网络。

第二十课

这节课讲的是左边两DDR的等长(2)

第二十一课

这节课讲的是左边两DDR的等长(3)

第二十二课

这节课讲的是右边的两DDR的拉线,。

1、把左边两片 DDR 的中间的过孔和走线复制到右边的两个 DDR,这个是左边做完等长再复制,能减少很多工作量,然后重新设置 T 点和规则管理器。地址线需要重新走的。

我的思路:

a、将原点设为DDR的中心

b、随便找一个过孔,看它的坐标

查看第 3 片DDR的坐标:(1070.00 0.00)

纵坐标保持不变,横坐标根据情况加或减。

得到另一个过孔坐标(1056, -362.20)(因为这个过孔在原点的左边)

c、选中要复制的过孔和走线,

执行复制命令(自定义快捷键m)

d、复制命令面板选择:自选复制点

输入它的坐标 x -14.00 -362.20

e、输入坐标 x 1056 -362.20

看到20:25,剩下 的是右边的走线。

第二十三课

没看,讲的是右边DDR地址线的等长。

第二十四课

没看,讲的是右边DDR数据线的等长。

第二十五课

第三十一课

第六十八课

线的等长,大多数人往往只考虑 PCB 上布的线的等长。

但重要的是,必须考虑芯片内部的线的长度,可能不是等长的。

要在画等长之前就设置好参数。

设置参数也要小心,要是设置错了,那完蛋了。

芯片内部没有做等长,并且不能通过软件调整的话,它会提供一个表,比如 RK3399_SOC_Package_Pin_Delay_V1.0_20161103.pdf 文件中:

长度能差到 2.6 mm,接近100mil了,再加上PCB上的走线误差,DDR 时序绝对会出问题。

所以一定要清楚芯片内部有没有等长。

一般厂家都会提供 Excel 表格形式的文件。

画等长的时候会显示该参数:

对一些引脚添加 Pin Delay 参数:

Pin Delay 导出:

【File】【Export】【Pin Delay】然后点击元器件,输出一个 csv 文件。

瑞芯微没有给出管脚名,只有网络名,所以还是有点麻烦的,可以借助 Pads 导出网络名和管脚。

其实就是借助元件的管脚信息:给它按照网络名排序然后复制到excel中

挑关心的管脚,还得把mm转换为mil。

Allegro mil 的小数点后取两位。

搞成这样的形式,生成逗号分割,然后导入到Allegro:

【File】【Import】【Pin Delay】

对于瑞芯微 RK35 的芯片,在 Official Release/Common Document 目录下,

不同芯片有不同的文档命名,比如:

Pin Delay

Pin Out

Pin Length

全志的好像不需要

可以参考别人的设计:

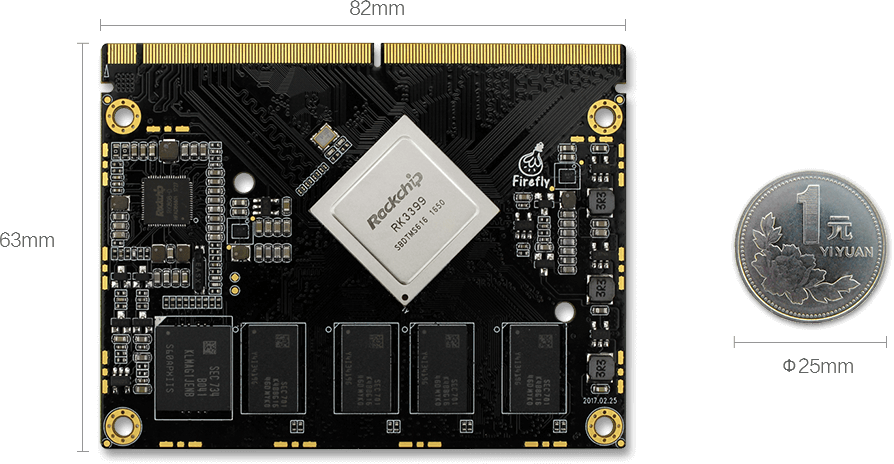

RK3399核心板 Core-3399J 六核64位高性能核心板

多层板的概念与层叠结构解析

在设计多层PCB电路板之前,设计者需要首先根据电路的规模、电路板的尺寸和电磁兼容(EMC)的要求来确定所采用的电路板结构,也就是决定几层板,确定层数之后,再确定内电层的放置位置以及如何在这些层上分布不同的信号。这就是多层PCB层叠结构的选择问题。

层叠结构是影响PCB板EMC性能的一个重要因素,也是抑制电磁干扰的一个重要手段。本节将介绍多层PCB板层叠结构的相关内容。

1.层数的选择。

电路的规模、电路板的尺寸、电源和地的各类、板线工作频率、特殊布线要

求的信号数量、性能指标来确定板子层数。对于一些EMC指标苛刻的产品在成本

能随的情况下,应当适当的增加地层。

2.POWER、GND的层数

POWER:单一电源和多种互不交错的电源(电源层分割)有一个电源层即可;·

多种电源相互交错可用2个或多个电源层相邻层的关键信号不跨分割。

首先看CPU和连接器的线好不好练

大致评估:

板子尺寸,越小越难布线

元器件数量,越多越难布线

CPU和连接器(排针、金手指等)的交叉程度,越顺越容易布线

难度越大,用到的层数越多。

评估 BGA 芯片所需要的层数,在不考虑外围交叉线的情况下:

引脚 0.65 mm以上的间距,第一第二排是可以直接在顶层拉出来的:

如果第二排有空引脚的话,第三排也有可能拉出来。

Allegro 空脚颜色设置,7分钟左右。