这篇文章中说的都是 10/100 M 的电路,不涉及 1000 M 的电路。

参考资料:

YT8512H

RMII 接口:

9 根线

MCU (MAC) PHY(YT8512H)

┌────────────┐ ┌──────────────┐

│ │ │ │

│ TXD0 ─────┼──────────▶│ TXD0 │

│ TXD1 ─────┼──────────▶│ TXD1 │

│ TXEN ─────┼──────────▶│ TXEN │

│ │ │ │

│ RXD0 ◀────┼───────────│ RXD0 │

│ RXD1 ◀────┼───────────│ RXD1 │

│ CRS_DV◀────┼───────────│ CRS_DV │

│ │ │ │

│ REF_CLK◀───┼───────────│ REF_CLK │

│ │ │ │

│ MDC ─────┼──────────▶│ MDC │

│ MDIO ◀───▶│───────────│ MDIO │

└────────────┘ └──────────────┘电路设计

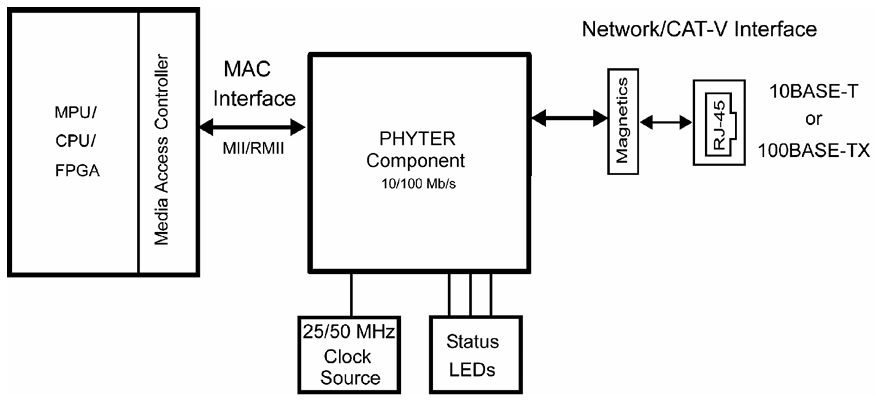

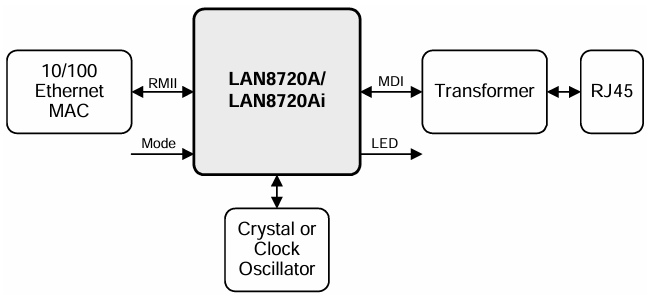

以太网电路结构:

大多数都是25MHz的晶振

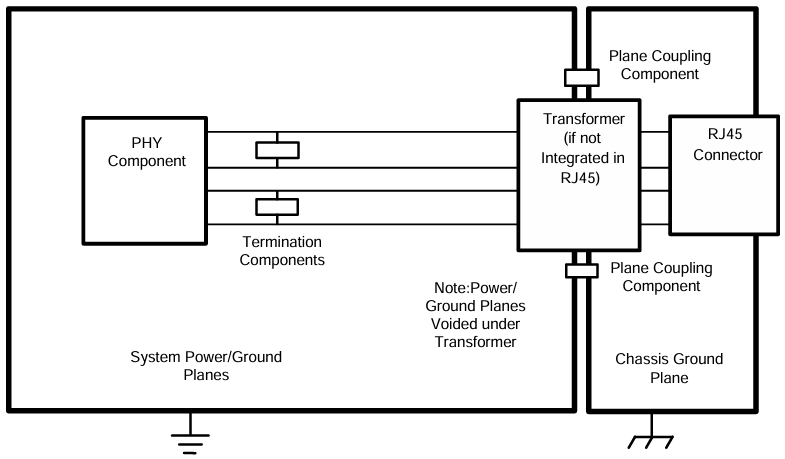

PHY 连接变压器,变压器连接 RJ45 电路参考:

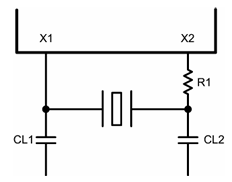

晶振电路:

推荐使用 25 MHz 20pF负载的晶振。

振荡器电路最小驱动功率为100 µW,最大为500 µW。如果晶振规定的驱动功率较低,应在X2与晶体之间串联一个限流电阻。

一般来说,R1 不用。

PCB 设计

MDI 差分对:连接 RJ45 座子的,TX+、TD-、RX+、RX- 共 4 根线。

以前的是单端 50 Ω 对地阻抗,现在都是 100 Ω 差分阻抗。

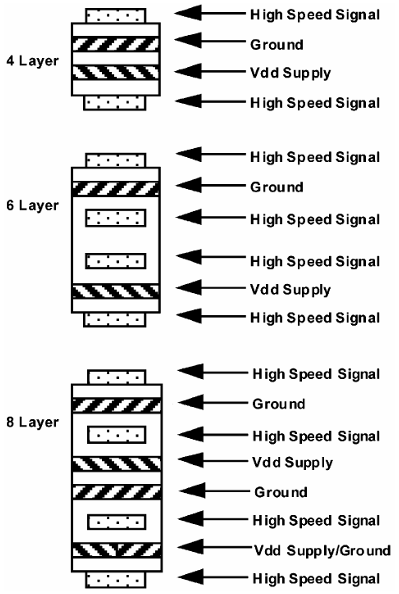

(1)为了满足信号完整性和性能要求,建议至少使用四层 PCB。推荐的四层、六层和八层板的层叠结构如下(也可以采用其他选项):

MDI 不换层、不打孔、不跨分割,走顶层。

RGMII 走顶层和3层。

RGMII 是单端 50 Ω,每一组的长度在 25 mil内。组间不要求。

(2)Layout 案例:

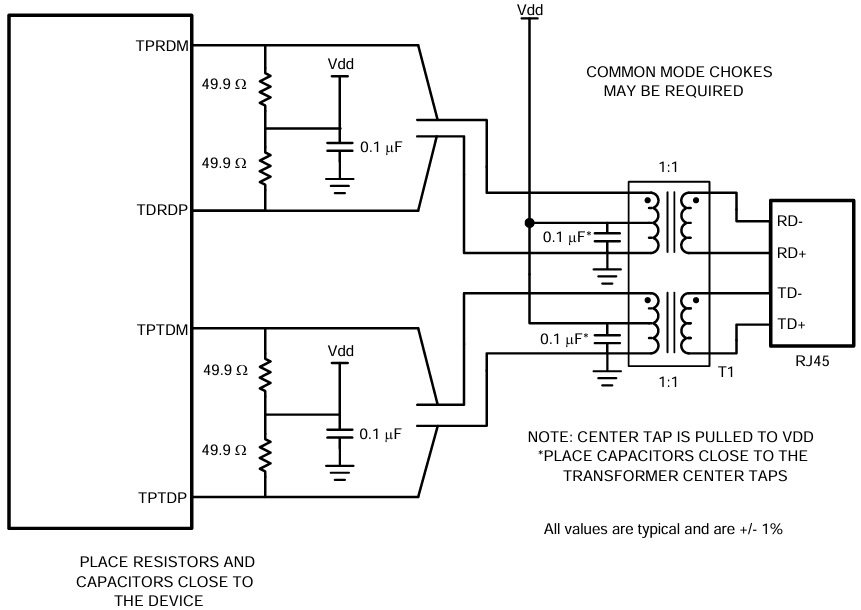

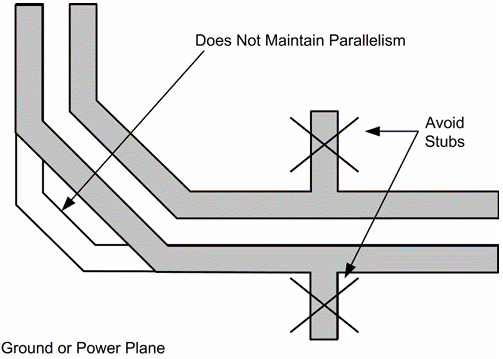

(3)将49.9Ω、1%的电阻和0.1μF的去耦电容放置在PHYTER的TD±和RD±引脚附近,并通过直通方式连接到Vdd平面。在所有信号线路上,应避免出现分支,尤其是差分信号对。参见图7-11。在差分信号对中(例如TD+和TD-),线路长度应保持平行并匹配。匹配的长度可以最小化延迟差异,避免共模噪声增加和电磁干扰增强。参见图7-11。

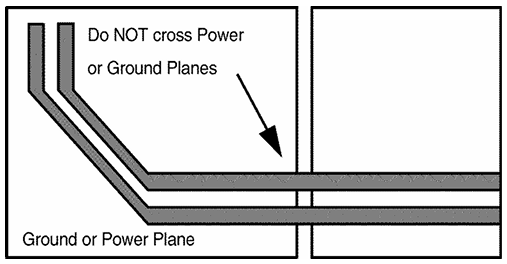

(4)理想情况下,信号路径上不应有交叉或通孔。通孔会产生阻抗不连续,应尽量减少。如果可能,尽量将整条线对布设在同一层。PCB走线长度应尽可能保持最短。信号走线不应跨越平面分割。如下图所示。信号跨越平面分割可能导致不可预测的回流电流,并可能影响信号质量,同时可能产生电磁干扰(EMI)问题。

(5)电源

器件的 Vdd 电源引脚应使用低阻抗 0.1 μF 表面贴装电容进行旁路。为了减少电磁干扰(EMI),电容应尽可能靠近组件的 Vdd 电源引脚放置,最好位于电源引脚与连接到电源平面的通孔之间。在某些系统中,可能需要在电源引脚串联 0 Ω 电阻,因为电阻焊盘在需要添加 EMI 阻尼珠以满足系统级认证测试要求时提供了灵活性。(见图 6.8)建议 PCB 至少具有一个完整的地平面和一个完整的 Vdd 平面,为元件提供低阻抗电源。同时,这也为非差分数字 MII 和时钟信号提供低阻抗回流路径。还应在 PHY 元件附近放置一个 10.0 μF 的电容,用于 Vdd 平面和地平面之间的局部大容量旁路。

Layout 设计规范:

(1)对于四层板(Top-Gnd02-Power03-Bottom),在整个以太网电路(RJ45、变压器、芯片)下方,Gnd02的区域要保证完整的地平面,不能跨电源分割。来保证完整的参考平面。

(2)MDI 差分对的差分阻抗 100 Ω,差分误差 5 mil 以内。

(3)MDI 两个差分对之间的间距 3W 以上。

()差分对之间的长度差 25 mil左右,100M的50mil也可以。

(4)时钟线要短,包地

(5)同组内误差 50 mil以内,组间不要求。

(6) RGMII 下面的地平面也要完整。

(1)传统设计中,RJ45接口 + 网口变压器 + ,现在室内的设备不需要挖空了,要挖空也行。

(2)PHY 到 RJ45 的RX、TX,两对差分对,。两对的长度差在 5 mil 以内,这个不清楚,好像也不用吧。

(3)

(4)

(5)

(6)

(7)

串联电阻