第十五课

电源输入的电容要靠近主芯片放。

从电源芯片出来,电容从大到小。

mark点和螺丝孔都可以作为独立的元件,画在原理图中

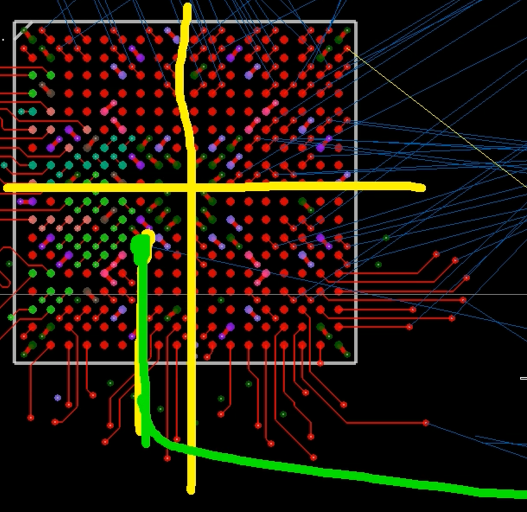

pads logic中暗色主题下,选中网络,看的比较直观舒服

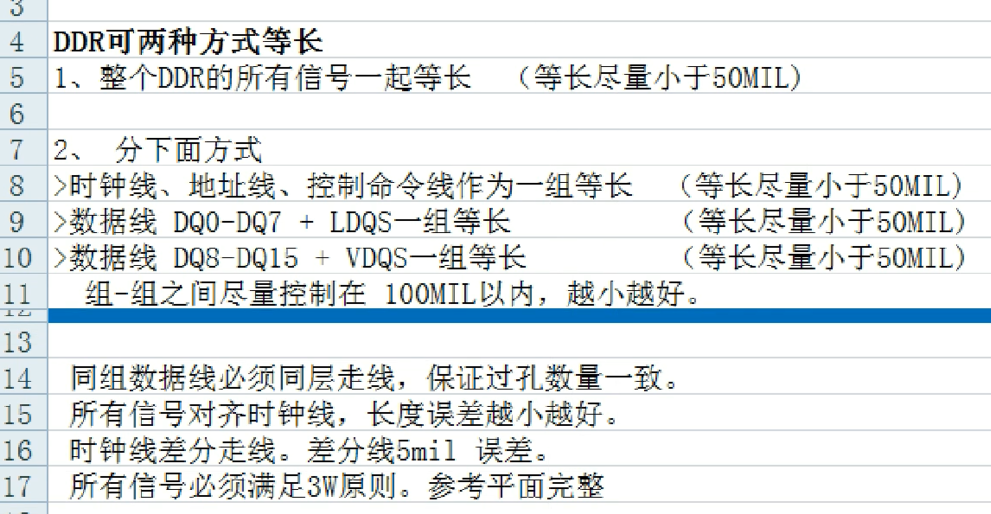

DDR:

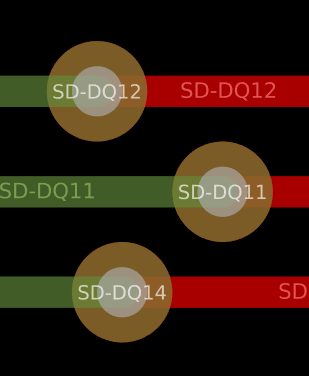

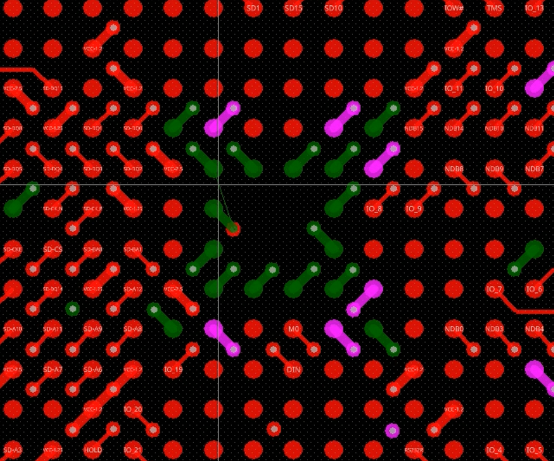

DDR的数据线16根,分为两组,一组8根,走线的时候分组分开走。

DQS、DM线跟着分组,也就是一组10个。

同组同层走线,有一根线要换层,所有线都得换层。也可以说,每根线的过孔数量要一样。sdram速率比较低,可以不这个要求。

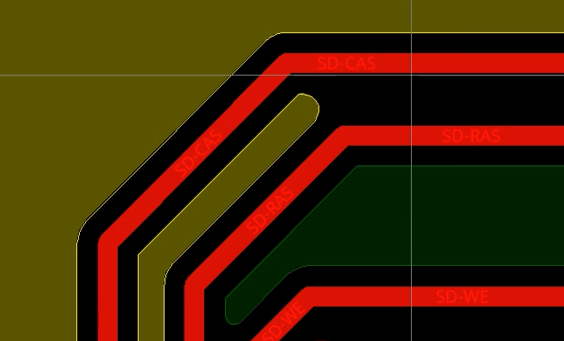

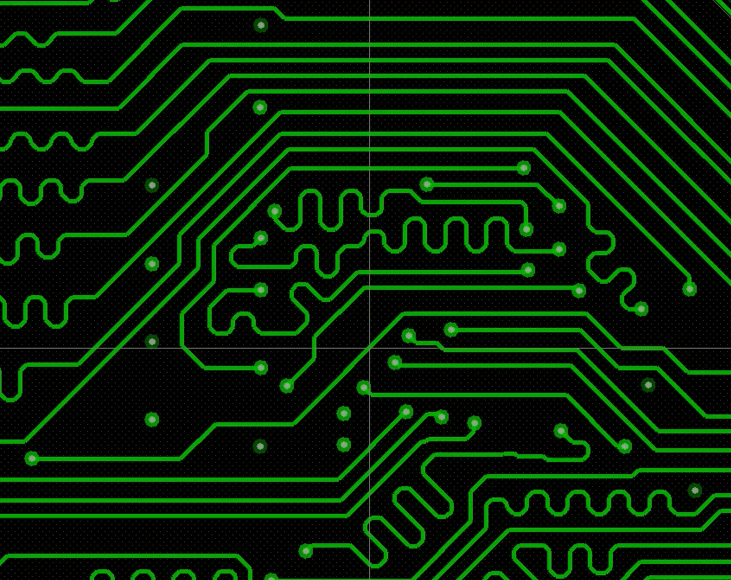

SDRAM速率比较低,可以不做等长,但是ddr要做等长。

除了上面的数据线16个、DQS、DM,其余的作为一组,做等长。这些线不同类型之间不用同层,过孔数量不用一致。

DDR的所有走线要满足3W原则,从线中心到中心要满足3倍线宽。能4W最好。

DDR的所有线,必须要完整的参考平面,不能有跨分割区域的情况。

DDR参考电压,走线最小8mil,最好20~30mil

DDR的话,信号看DQS对齐。SDRAM,信号看时钟线对齐。

DDR3以上,建议等长小于25mil

fpga大部分都是通用的引脚,除了少数特殊的引脚。

小设备一般用flash,像手机等大容量设备,用emmc,存储

spi走线没什么要求,速率低

拨码开关、跳线啥的,这些开关没有要求,连上就行

BUF原理图,使用芯片增强IO口的驱动能力(电流)。如果使用上拉电阻的话,功耗会增加,而且可能会造成信号失真。

第十六课

百兆网口

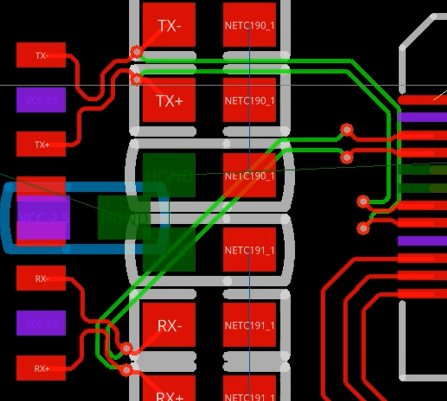

2对差分对,100欧姆差分阻抗。

RJ45座子分为两种,一种是含有网口变压器,一种是不含网口变压器,含变压器的贵。

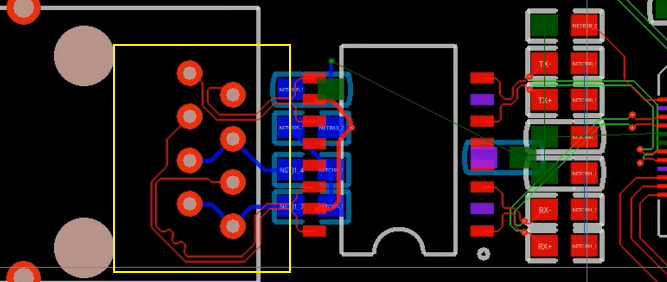

RJ45座子和网口变压器芯片(芯片连接rj45的那一半)所在的区域,下面所有层不能铺铜,并且走线不能打孔。

百兆的芯片,对走线没什么要求,靠近rj45就行了。

Allegro设置中指定封装的位置,放在最上面优先级最高,名字重复优先调用。

PCB设计要求

最小过孔,钻孔8*焊盘16mil

最小线宽、线距 5mil

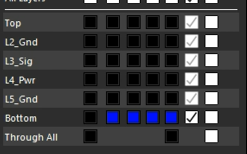

6层PCB,层叠结构:T G S P G B,6层板常用这个。S P 可以调换,如果B底层没有走线或走线很少的话。S和P之间越厚越好,抗干扰。有些公司使用假八层。

Allegro层叠设置中,除了修改层的名字和介质,其他的都不用修改,改了也没用,导出gerber文件的时候不会导出这个。如果是做仿真,需要认真填写这些参数。

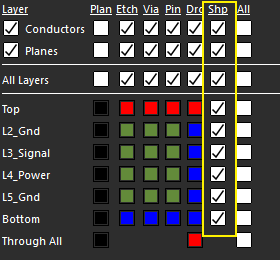

Gnd、Power设置为平面层,这样Allegro控制面板中方便显示和关闭,平面层就是铺铜用的。

负片现在基本上没人用了

Route Keepin,最小10mil,一般20mil

Allegro隐藏电源网络有两种方法

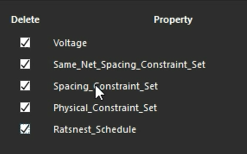

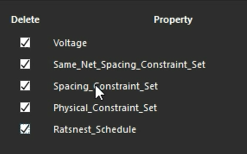

【Logic】【Identity Dc Class】,对电源网络,Voltage电压设置为0就行了。这样做的坏处是,管脚上有叉叉。

选择某一网络,右键【Property Edit】,这些删除掉,这是都是乱七八糟的属性。最关键的事No Rat属性,加上。设置完后,可给电源网络分配颜色,方便区分不同的电压,方便接线。

ctrl+左键,多选网络,统一操作属性

推荐的做法是,在导入网表后,全选所有网络,删除掉乱七八糟的属性。否则后面可能会出现奇怪的小问题。

Allegro与OrCad同步图标的必要性,52:00,Allegro中选择网络多的话orcad会卡死

USB50欧姆差分阻抗

有源晶振,加上一个电阻,是为了抑制时钟过冲,一般几十欧,典型的33R。甚至还会加一个pF级的电容接地。

布局前,同一模块的元器件放一起

第十七课

布局的时候,设置栅格,这样好摆放对齐一点。对于高层板中,因为元器件很小,栅格小一点,mil:2,mm:0.05。一般的pcb话4mil,0.1。

要考虑芯片的供电从哪里引入。这种不太好确定,一般都是预布局,走线的时候才能最终确认。

一般板子元件间距1.5mil,对于高密度的平板,一般0.8~1mil,对于手机版,0.5~0.8 mil

一些上拉电阻,可以放到背面去。

其实也没啥技巧,看情况放在背面。

按键没有固定位置的话,就放在板子边上。

Allegro中BGA先扇出、后扇出,都没有问题。

电源线宽一点

有的人画的原理图中,把所有的电容都放在一起了,这种傻逼的做法。当主控的电源引脚都有了电容后,多了很多电容,要观察有没有什么地方缺电容的,把电容放过去。电容实在多的放不下的话,可以放在电源的输入处。

第十八课

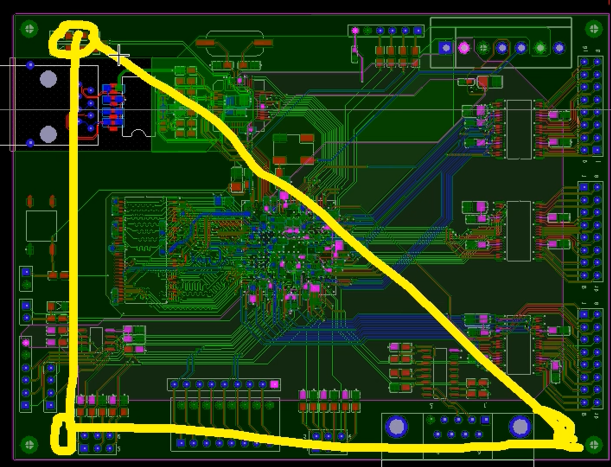

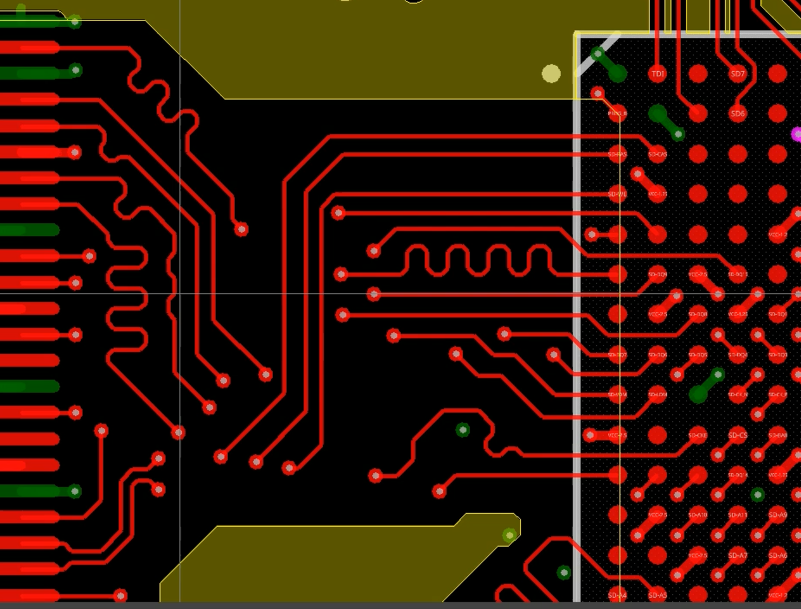

有sdram、ddr芯片的pcb,先画这个,然后画其他的。

Allegro中的Bus和NGrp网络组几乎是一样的,只有很小的不同,做等长的时候哪个都行。

Allegro给网络组All分配了颜色,走线、过孔啥的全部都是那个颜色了,Allegro软件的一个特色。颜色这部分乱七八糟的,取消勾选的话,还是会保留之前的颜色的,无法单独清除颜色,只能清除所有颜色。

Allegro在规则约束器中设置的线距,是从边到边的,不是中心到中心的!若两根导线宽为5mil,间距为10mil,则他们的中心距离为5/2 + 10 + 5/2 = 15mil,即3倍线宽,3W原则。

DDR先画数据线,数据线有两组,哪一组能更多的从顶层拉出来,就优先从顶层拉出来。这个不用注意顺序,先拉出来就行了,后面再处理。

从 BGA 引出的时候使用修线命令,会避让bga背面元件的焊盘(不过这个设置中好像可以关掉),造成走线困难。解决办法是使用move移动命令,并勾选【Slide etch】让导线跟着移动。

先把必须要打过孔的引脚(VCC、Gnd等;还有确定位置的电容电阻等,必须先打地孔)打过孔,后面走线时避让过孔。否则先走线后再打过孔的话,还要调整,工作量增加,降低效率!

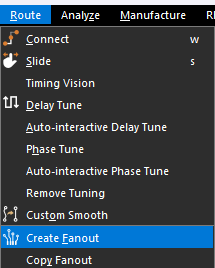

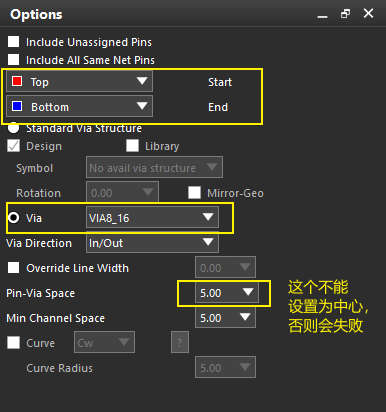

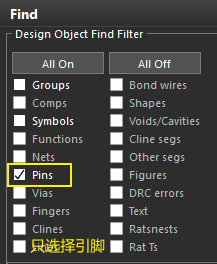

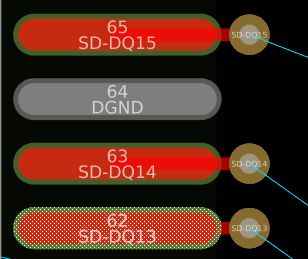

Allegro小技巧,管脚可单独扇出:

第十九课

大公司Layout和硬件是分开的,小公司的板子一般不会很复杂,大部分都是硬件一块搞了。

只做Layout走不远,必须会硬件。一个男的,只会Layout的话没啥价值,老板不如招个女的。硬件和画板不分开!!!

Allegro中空的网络是不会扇出的。

盲埋孔基本用不上,只有手机主板等高密度的产品才会使用到,甚至电脑主板都用不到盲埋孔。盲埋孔导致成本剧增。但是用盲埋孔画板子会简单很多。

想在技术群中接单子就是智障,狼窝里面找肉。

第二十课

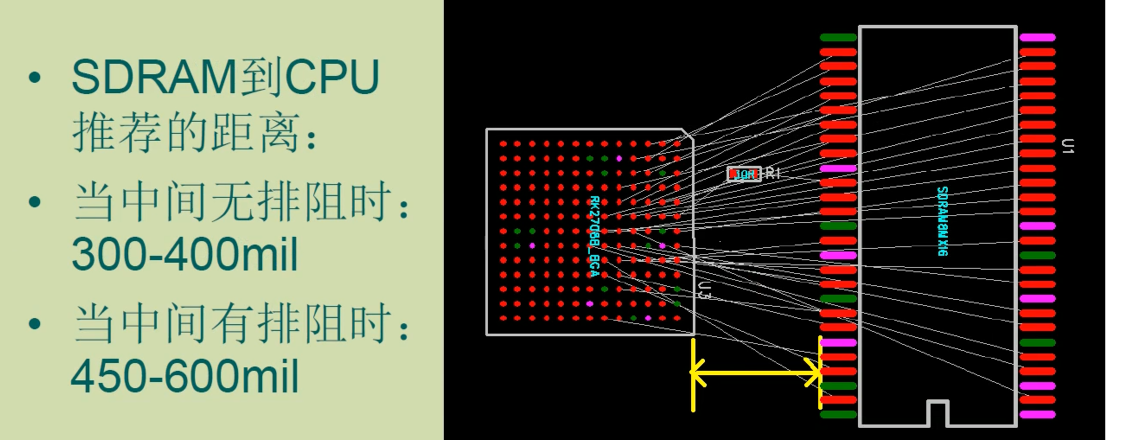

芯片和DDR的距离要求,参考老吴的高级班课程。肯定是越近越好。还有DDR之间的距离等。

把DDR的数据线全部接通,不用考虑啥的,接通就行,这是第一步,后面再考虑等长、规则等。现在把线拉好看的话就是浪费时间的,应为后面还要大量的调整。

高速信号要考虑信号回路的完整,注意平面分割的问题,下图这种叫连续打孔,不能连续打孔!!!简单的评判标准是,两个过孔之间最少要能穿过一根线(斜着)。垂直方向最多连续的过孔是两个,最好一个都不连续。

因为DDR和主控是水平数据流通的,不能垂直连续打孔,但是水平的三个连续的过孔是可以的,但是水平之间也不要太密了。

通常,布线的时候会不断地调整元件,这也就是画板子麻烦的地方,要考虑的东西多。

DDR还是最好走顶层和信号层,尽量少走底层。

高速信号最好走内层信号层,但是像6层板,它只有一个信号层,难免的会顶层走高速信号线。有钱的话高8层板会好一点。

第二十一课

绝大多数的芯片不需要填写 Pin Delay 参数(就是线在内部是多长的),除非官方说明了,导入既可。

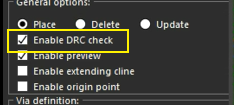

Delta:Toler 显示黄色表示规则未开启,右键 Analysis Mode 开启

DDR2、SDRAM 数据线控制等长误差在 50mil,DDR3误差25mil,越小越好。

板子小的话,难度会增加,因为没有空间去画线,误差没办法减到很小。

DDR 的地址一般误差200mil,但是推荐 100mil?????有这句话吗

先做空间小难度大的组的等长。

有些芯片可以修改延时,但是延时是有范围限制的,因此还是要做等长。

第二十二课

一般 4W距离啥的,目测就行了,没必要有那闲工夫一点点测量。

竖着绕不了,就横着绕。

第二十三课

1、不要直接出

要有一段距离

2、DDR部分可以用地线圈起来,但是该地线要离DDR 5W距离,一般也不用画,其它IO和这些线3W就行了。

3、高密度的板子在布线后,千万不要切换单位,否则可能会出问题。

4、先把bga用到的线都拉出来,然后看有没有能交换的。

5、背面有空间的话,优先把滤波电容放在背面,并尽量接近过孔,但不要压在过孔上。这样的话滤波电容离引脚更近,效果好。如果放顶层的话,电容要离芯片有1~1.5mm的距离,这样距离相对较远了,效果差一点。

6、多层板电源引脚可以先统一扇出

第二十四课

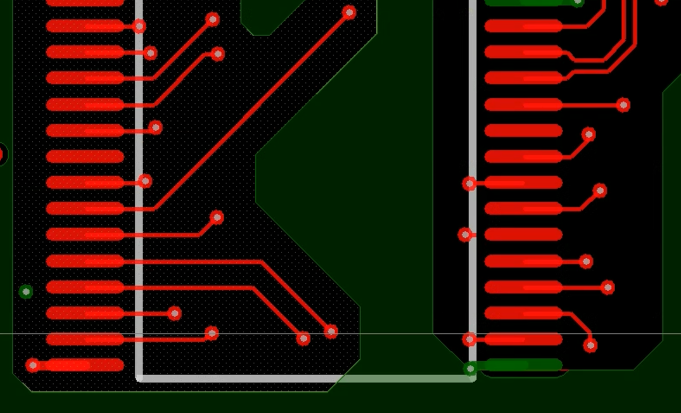

1、BGA芯片分为四个部分,每个部分先拉出来线,然后再转向。不要乱拉,否则里面容易堵死。

就是从最近的位置先从芯片中拉出线,然后再处理。

2、感觉没啥技巧,能从顶层拉出来就先拉出来。要是能从多个层拉出,就根据板子情况考虑一下呗。

3、有源晶振比无源晶振要求低,线长一点也没事。

4、晶振所在的层挖空,其它层不用挖空。晶振所在的层是绝对不能走线的,其它所有层尽量不要走线,如果是高密度的板子,实在走线走不下了,那就在第二层铺个地,然后第三层以后可以走线。

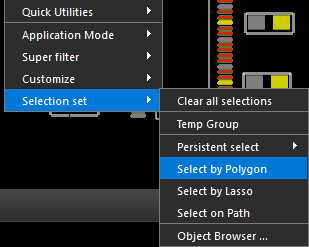

5、Allegro 区域选择,因为 Allegro 的选择框是方框,斜着的话选不了,多根走线的时候不好选择线头(这个要在走线的命令下)。这个常用于选择元器件。

区域、、路径

6、SDIO接口(SD卡、Wi-Fi)要做等长(一般200mil,通常50mil),时钟线(还是全部?没听清楚)包地。

7、4mil 生产技术二十年前就很成熟了。

8、细的线比粗的线抗干扰能力差

9、Nand Flash 不需要等长处理,因为速率比较低。Nor Flash呢,没讲清楚。

10、SDRAM压根不用做等长。

11、RGB24接口一般不用等长处理,时钟线建议包一下地。

12、音频,主要是防干扰,特别是模拟信号。

第二十五课

1、无源晶振的电容可以放后面也可以放前面

2、一般bga顶层拉线拉到第3层

3、变压器的输出端,网口的 RX+ 和 RX-差分对;TX+ 和 TX- 差分对,100欧姆阻抗,误差5mil。如果是外接变压器的,RJ45接变压器的也要差分对,和前面一样。TX和RX不用做等长的。

4、网口这样画也是可以的:

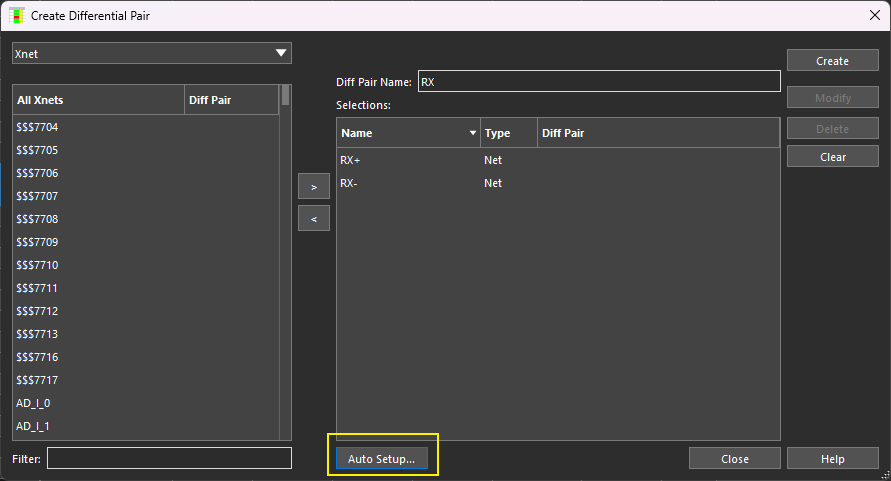

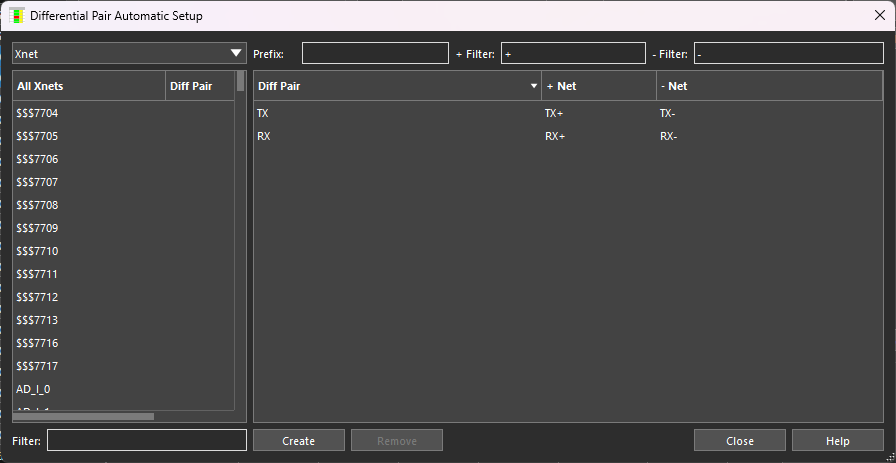

5、差分对可以搜索、批量设置

6、晶振的线建议6mil以上,一般8mil

第二十六课

1、网络线有8条,百兆网口只用到了4条,其余4条要避免悬空,防止干扰。

2、差分等长参考:

3、1、包地走线的两个原因:(1)这根线很敏感,怕受干扰(2)改善线的回路

4、电源板,难的不是拉线,是它的知识

第二十七课

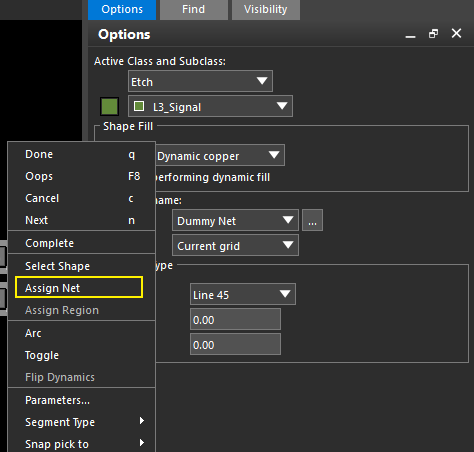

1、在铺铜命令下,右键可点击选择网络

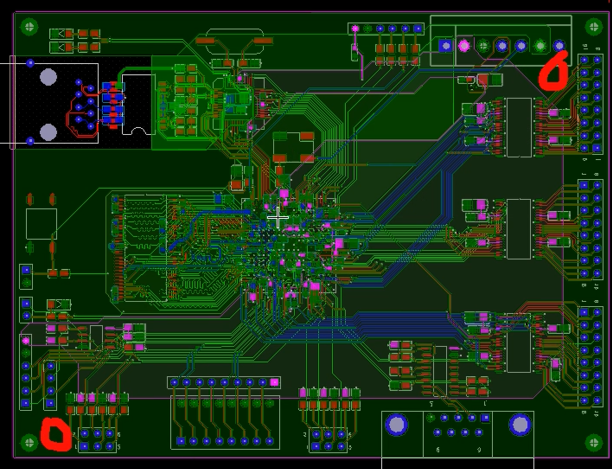

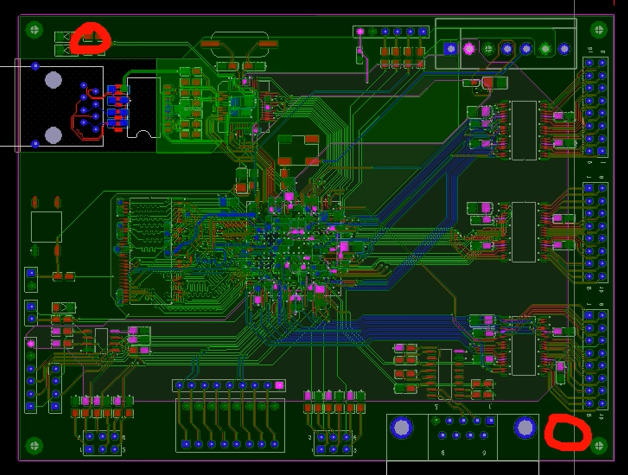

2、先整体铺铜。TOP、Bottom、GND层必铺,SIG层一般走线不多的话,也要铺。Power层就不用铺了。

3、Allegro 铜皮开关快捷键

4、一般都是先布数据线,然后电源,电源画铜皮。(布电源线的时候可以把电源网络设置颜色,其它网络颜色设暗一点。)可以单独显示 power 层操作。了。

5、Power 层电源不好处理,可以换到其它信号层(非GND层)处理部分电源。

6、芯片的参考电压,对电源的要求比较敏感,走线要宽一点。长线20~30mil;短线,10~15mil也行。

7、DDR芯片的参考电压,不能直接在sig层下面的power层画线或者铜皮,会造成参考平面分割,因此这里只能从底层拉出。底层拉不出来的话,整个DDR需要重新等长布线,那就麻烦了,666。

DDR 芯片,在走等长线的时候就应该考虑电源的问题,通常在信号层画。

必须提前考虑,否则后面可能要推倒重画。

8、太远的话就不要画铜皮了,直接走线。铺铜主要是BGA和DDR的区域。

9、计算阻抗的时候,尽量让要用到的层的线宽保持一致,通过不同间距。

第二十八课

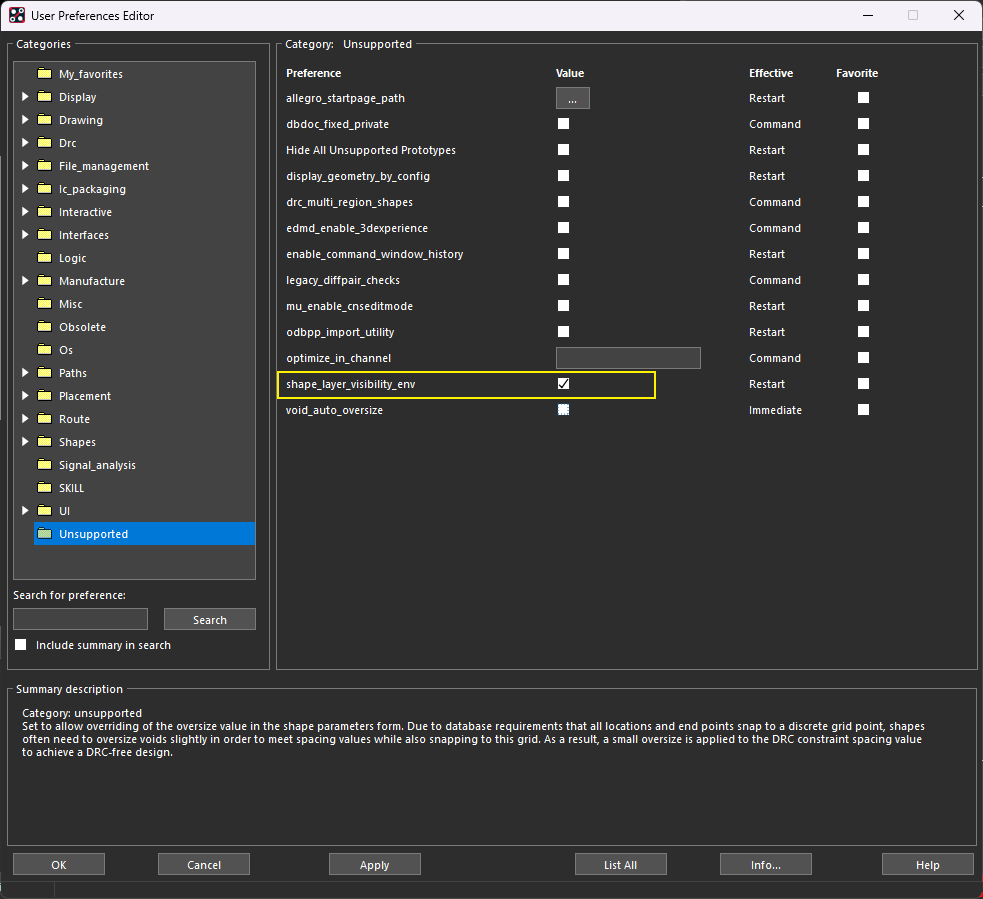

1、打开每一层的铜皮显示开关,重启后生效

2、电源层最外一圈最好包地。

3、BGA 背面的滤波电容,线宽 8 ~ 15 mil

4、1oz 1A 建议 1mm 以上

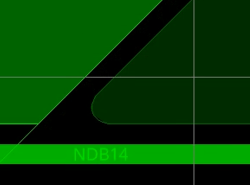

5、从变压器中间到网口,所有层铜皮挖掉。

6、它这个铺地好像是除了电源层都铺,因为其它层都是空着,不铺白不铺。

7、如果实在要在 GND 层布线或铺铜,应选择参考少的 GND 层。

8、电源铜皮之间建议8mil以上,其实再小一点也没事,符合板厂生产就行了。220V强电需要考虑爬电距离。

9、在 TOP 层不容易看清漏接的线,飞线,换个线少的层看,有打孔的话。

10、用于贴片时的光学定位,一般产量少不用加。

mark点的要求:

一个板子两个mark点,斜对角放:

mark点围成的区域,尽量包含所有的元器件。

3个mark点:

顶层和底层的mark点可以重叠,也可以不。

11、以太网为什么要挖空?

早期的网线经常在户外拉,比如两栋楼之间,因此需要注意雷击。

雷击电压大,就想你通220V电一样,会爬电,把整个电路板烧了。

其实对于现在室内的应用场景,不挖空都行。

所有层挖空

外接变压器:挖空 RJ45 和变压器

集成变压器:挖空 RJ45 座子

其实应该加 TVS 和防雷击的措施。

12、3225-4p的贴片晶振,top层要挖空,不要有走线和过孔,因为这种晶振底部不是金属的,下面放金属可能影响精度。其它层要不要都挖空,到现在都是一个有争议的话题,反正老吴是不挖空的。HC-49s这种贴片或插件的晶振,整体都是金属的,因此不用挖空。

挖掉的人有一种说法:防止电路板其它元件发热传导过来,造成工作异常。

13、DC-DC电感只需要挖空顶层就行,下面不要走线和过孔。

14、晶振周围如果有很大空间的话,可以不用包地。如果是高密度的板子,晶振旁边都是信号线,那就需要包地处理。

15、 绝大多数PWM和ADC随便画就行了,除非要求特别高,比如高速高精度,这种一般专精行业才会用到,普通场景不用考虑。

第二十九课

1、BGA封装的的 Top 层不要铺铜!因为里面的铜皮是非常不均匀的,造成焊接时受热不均匀,会增加损坏率。

两种方法:

(1)直接挖空,如果之前有铺铜的话。(这种方式挖所有层的话要一个一个挖)

(2)设置禁止铺铜区域(这种方式挖所有层的话一下子就行了)

2、DDR的区域也要挖空,所有走线的层。

因为铜皮不均匀的话,一段有铜皮一段没铜皮,阻抗会发生变化,阻抗不连续。

其实对于所有需要阻抗的线,都要注意有没有铜皮干扰,要么线两边都有铜皮(这种很难实现),要么都不要有。

铜皮要距离DDR线 3W以上。

3、我觉得有的电源线,不要直接画在power,否则后面电源平面分割的时候,可能出现问题。应该画在走线层。

4、有空的地方可以放置地缝合孔,用大一点的过孔,不要用小的。过孔可以直接复制粘贴。

5、差分线外面有空的话可以包地,包地的地线要大于8mil,太小的话会引入干扰。

第三十课

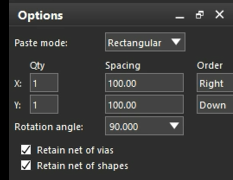

1、缝合孔,板子比较空的话直接使用阵列式打孔,密度高的板子手动打孔。一般间距 100mil 以上。

一定要打开这个:

Allegro批量打孔有个缺点:通孔焊盘不会自动避让,过孔可能会直接打在通孔焊盘上。

2、导线之间的铜皮,这种细长的信号线,可能有天线效应,有电磁辐射问题。

解决方法:(1)调整线给它消灭掉(2)增大导线之间的间距,让铜皮变大一些,最好再打上几个过孔(3)设置禁止铺铜区域

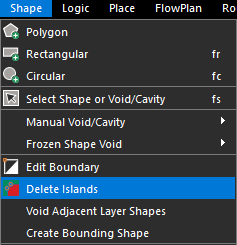

3、删除孤岛

4、尖角铜皮最好打过孔

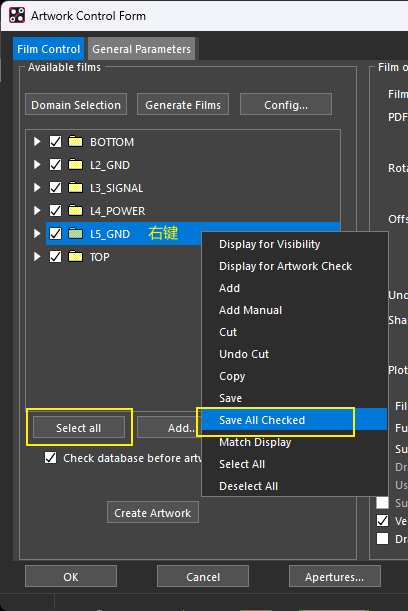

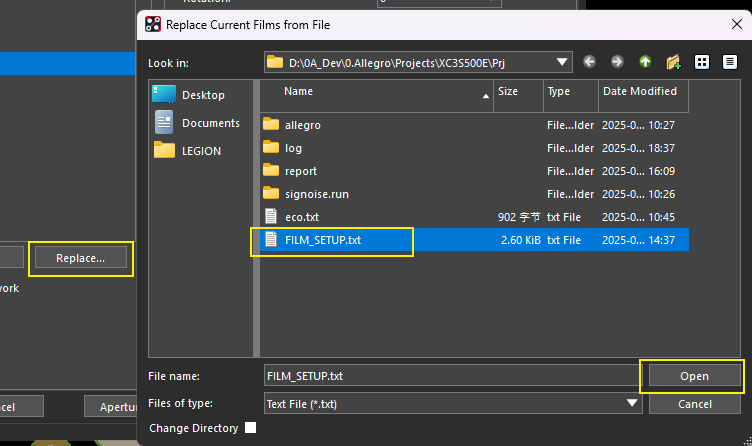

5、Film文件的保存与导入

保存:

导入:

6、Allegro的泪滴效果太丑了,所以没人用。AD和Pads添加泪滴多。

7、凡是涉及到时序的高速信号都要做等长

8、复制铜皮和过孔时,下面的选项为是否复制网络。