AD7606BSTZ:16 位 8 通道同步采样,200 kSPS

AD7606BSTZ-4:16 位 4 通道同步采样,200 kSPS

AD7606BSTZ-6:16 位 6 通道同步采样,200 kSPS

接口:

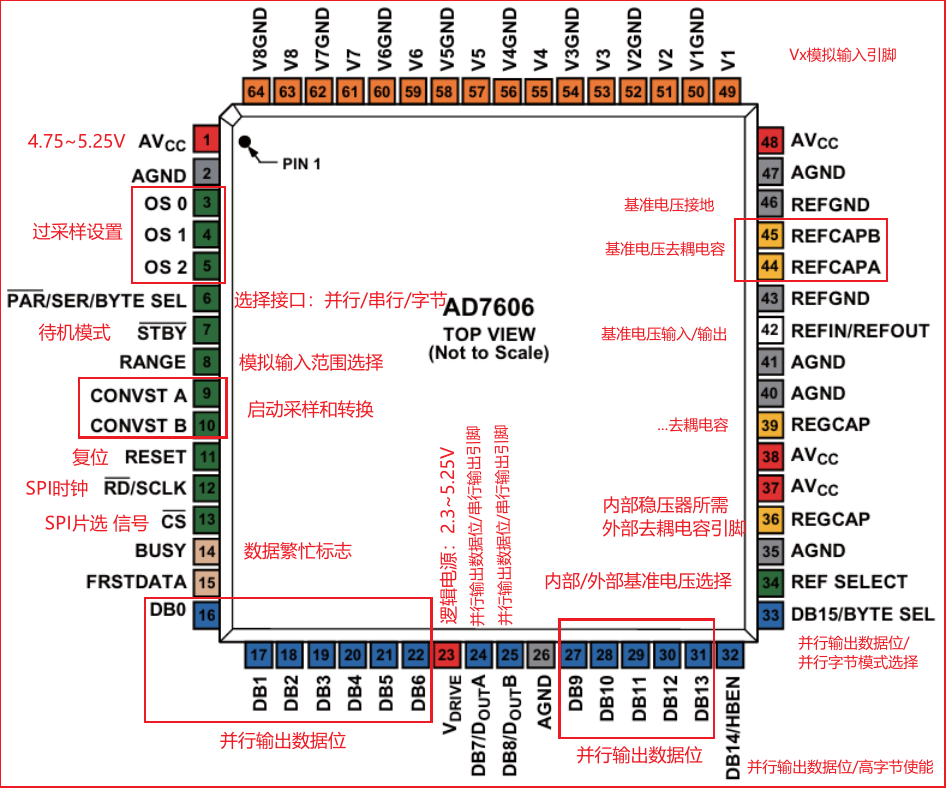

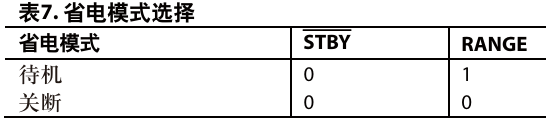

引脚说明

这颗芯片是非常经典的ADC芯片,现在的芯片都是用内部的寄存器配置,这个是引脚配置功能。

引脚说明,这里只考虑 SPI 串行方式:

编号 | 引脚 | 功能 | 说明 |

|---|

| AVCC | 模拟电源输入 | 4.75~5.25 V |

| AGND | | |

| OS 0、1、2 | 过采样模式设置 | |

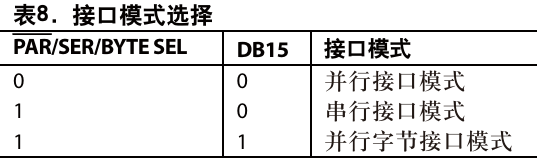

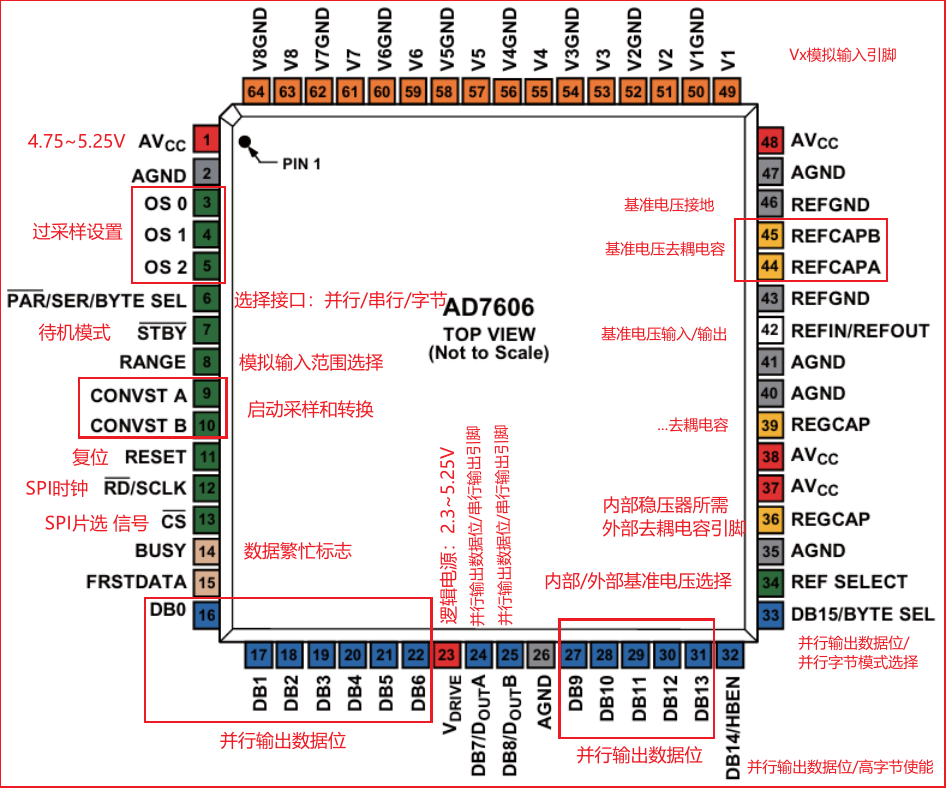

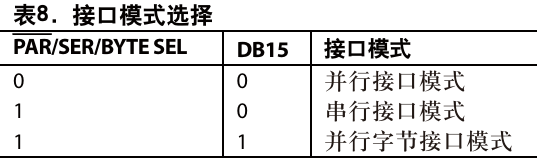

| PAR/SER/ BYTE SEL | 通信接口选择(并行、串行、字节) | |

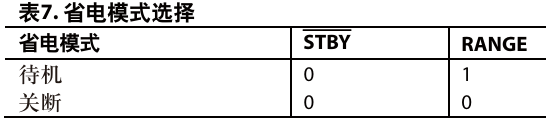

| STBY | 省电模式选择 | |

| RANGE | 通道输入电压范围选择 | 当 STBY = 0 时: |

| CONVST A, CONVST B | 开启通道转换 | 通常将这两个引脚连起来,统一控制所有通道。 |

| RESET | 复位 | 拉高电平,上升沿复位,最少 50 ns。 |

| RD/SCLK | | |

14 | BUSY | 输出繁忙指示(数据可读指示) | 转换开始后变为高电平,所有通道转换完成变为低电平。 |

15 | FRSTDATA | 并行模式下有用,spi模式下保持悬空,不要接GND。 | |

| DB0~6 | 7 根并行数据线 | |

| VDRIVE | 数字电源输入 | 2.3~5.25 V,推荐5V |

| DB7/DOUTA | | 并行:第 8 根并行数据线 串行:输出顺序 V1、2、3、4、5、6、7、8

|

| DB8/DOUTB | spi 模式下,如果不用这个,不能把它接地,悬空既可。 | |

| DB9~13 | 5 根并行数据线 | |

| DB14/ HBEN | 第 15 根并行数据线 | |

| DB15/ BYTE SEL | 第 15 根并行数据线 | |

| REF SELECT | 2.5V 基准电压选择 | |

| REGCAP | 内部稳压器外接滤波电容 | 1uF 到 AGND |

| REFIN/ REFOUT | | 内部基准电压:输出 2.5V 外部基准电压:输入 2.5V

10uF 到 AGND |

| REFGND | | 接 AGND |

| REFCAPA, REFCAPB | 基准电压外接滤波电容 | 这两个引脚接在一起,并接 10uF 电容到 AGND |

| | | |

转换采用内部时钟,AD7606 所有通道的转换时间为 4 μs,AD7606-6 为 3 μs,AD7606-4 为 2 μs

在 BUSY 下降沿的时候,输出数据寄存器将被替换为新值,除此之外任何时候都可读,因此转换期间也能读取数据。

不使用的模拟引脚要接AGND。

所有的通道都会转换的,不管使不使用。

省电模式

AD7606、AD7606-6、AD7606-4 的区别在于通道数不同:

引脚 | AD7606-6 | AD7606-4 |

|---|

49 | V1 | V1 |

50 | V1_GND | V1_GND |

51 | V2 | V2 |

52 | V2_GND | V2_GND |

53 | V3 | AGND |

54 | V3_GND | AGND |

55 | AGND | AGND |

56 | AGND | AGND |

57 | V4 | V3 |

58 | V4_GND | V3_GND |

59 | V5 | V4 |

60 | V5_GND | V4_GND |

61 | V6 | AGND |

62 | V6_GND | AGND |

63 | AGND | AGND |

64 | AGND | AGND |

SPI 协议电路:

数据输出

转换时间

参考电路