八、DDR3 T型拓扑布线流程

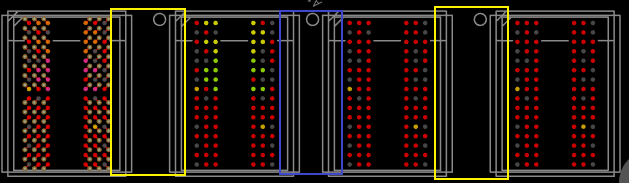

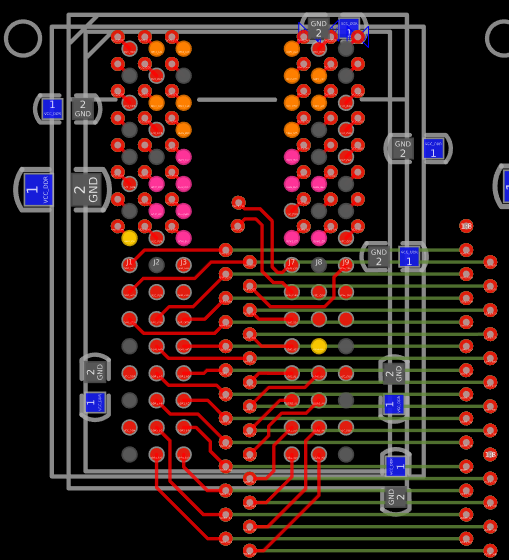

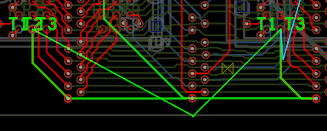

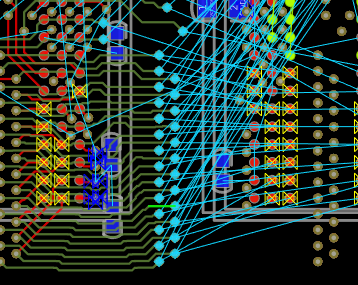

4 片 DDR3,T 形拓扑,过孔对齐,标准等长。

(1)等间距放置 DDR

左边两片构成一个通道,右边两片构成一个通道。

黄色框住的 DDR 的间距要相等,并且不能太窄,因为是主要走线的。

蓝色框住的 DDR 的间距可以窄一点,因为不是主要走线的。

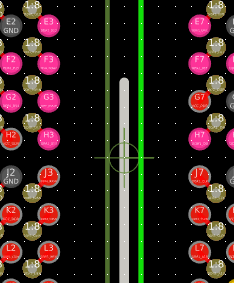

(2)确认过孔间距

1、栅格设置为 1mil

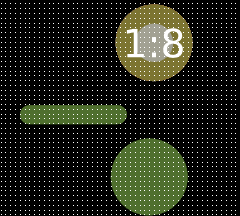

2、画一条线和两个过孔(就是DDR扇出的那个过孔)

3、移动过孔,放不下走线会缩回去:

就是找到一个线能放下的临界过孔间距:

4、 查询两个过孔的 Y 轴坐标差,这里是 29 mil

要取一个整数,先试试 28,28 不行就30。

测试的话两种方法:

第一种就是将一个过孔移动到指定的坐标,比如原来(163, -329) 移动到(163,-328)。看这个线会不会缩,或者DRC报错

第二种就是设置栅格,移动过孔到栅格上,然后从中间走线,能正常穿过就OK了。

这里发现 28 可以。

5、设置 PCB 原点为 DDR 的中心

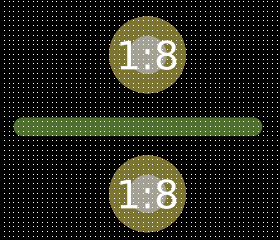

6、设置栅格为 14 mil,因为过孔要交错放置,所以设置为 28 的一半。

(3)放置过孔

DDR 内、两个DDR之间,都是在中心位置。

1、画一条辅助的 2D 线,线宽为8mil

2、这个芯片的地址组共8行引脚,一般取中间位置,这里第4行作为水平线,没啥原因,好看而已。

设置原点为(-14,第4行的Y坐标)

DDR 扇出的过孔、中间公共的过孔,这些都不是一劳永逸的,要在走线的时候实时调整位置的,这是一个麻烦之处。

3、

按栅格两边各走线

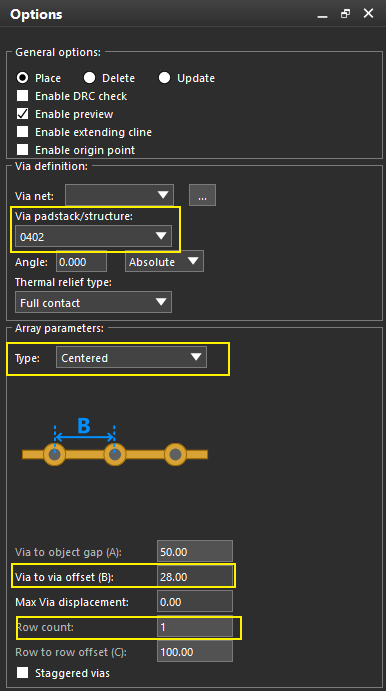

过孔不多,手动放置就行了,也可以使用过孔阵列(先画线,在线上打孔):

【Place】【Via Array】

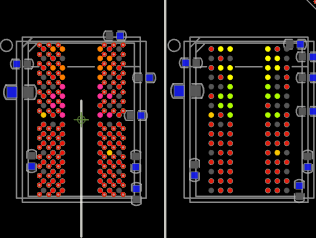

(4)连接管脚

1、先别管什么,引脚全连接上

复制过去:

走线的时候给数据组的过孔和飞线设置为黄色,比较清晰。

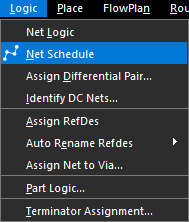

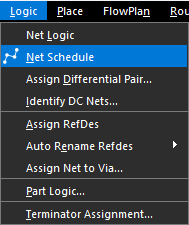

设置拓扑结构

有两种等长方案:

CPU 到 DDR 的总长度等长就行了,不要求T点到所有DDR的等长。这个简单点。

CPU 到 T 点等长,T点到所有DDR的等长。这个麻烦。

(5)设置 T 点

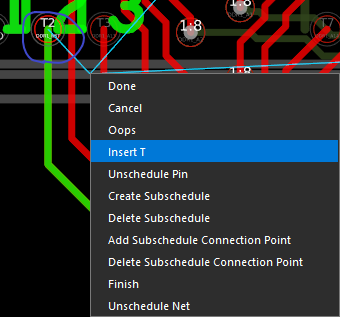

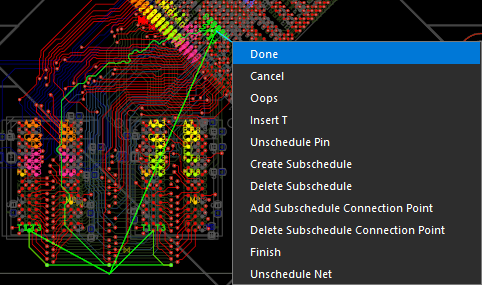

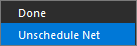

点击焊盘,选择网络,然后右键【Insert T】

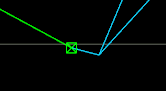

在中间位置空白处点击一下:

然后点击另一个管脚:

现在是在右边,要回到中间,因此再点击一下中间:

点击 SOC 上的引脚,最后再 Done 完成。

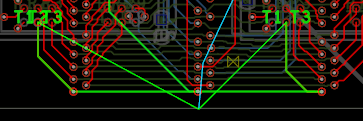

显示 T 点

这个 T 点是飞线,把飞线打开就能看见T点了。

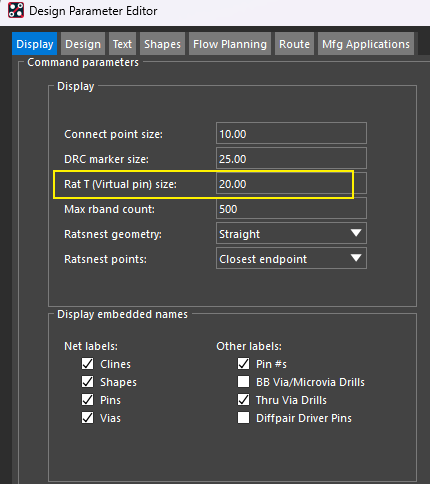

设置 T 点大小:

删除 T 点和等长约束

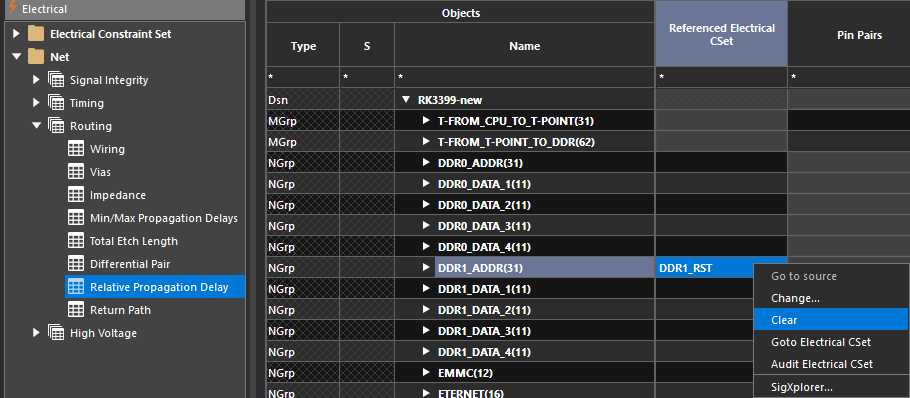

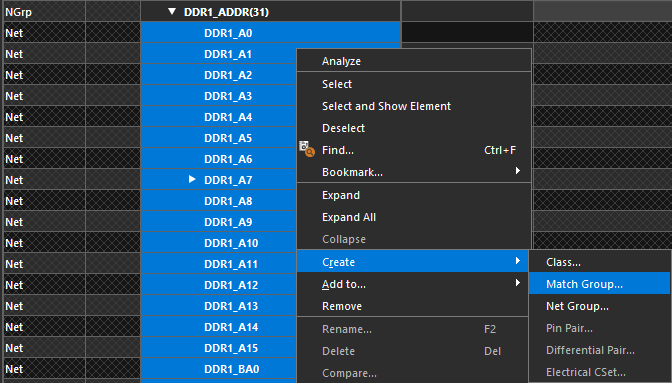

(1)把地址线分配的分组,右键 Clear 清除

(2)删除 T 点

在空白处右键选择:

点击 T 点。

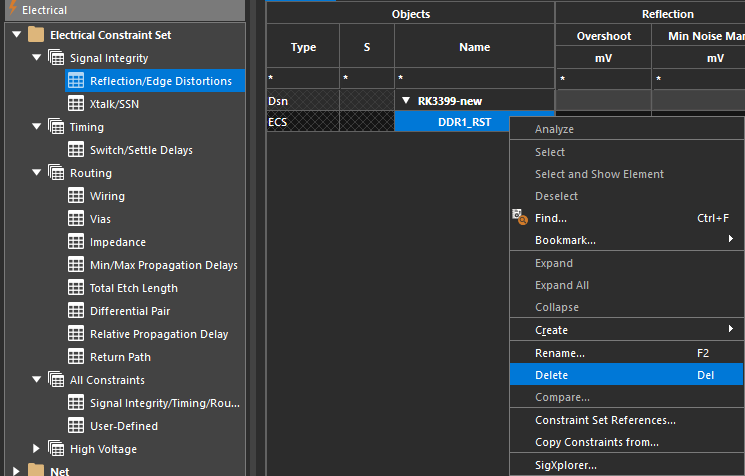

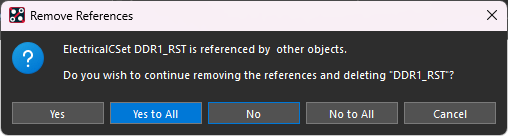

(3)删除约束规则

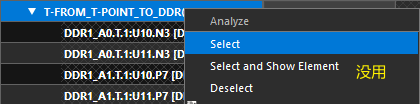

T点的颜色指示器,使用规则管理器中的 Select 是没有用的,只能手动框选网络。

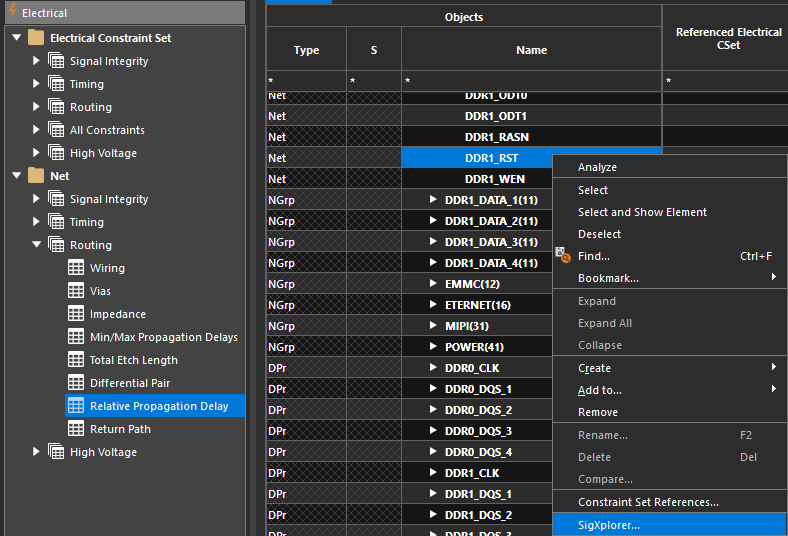

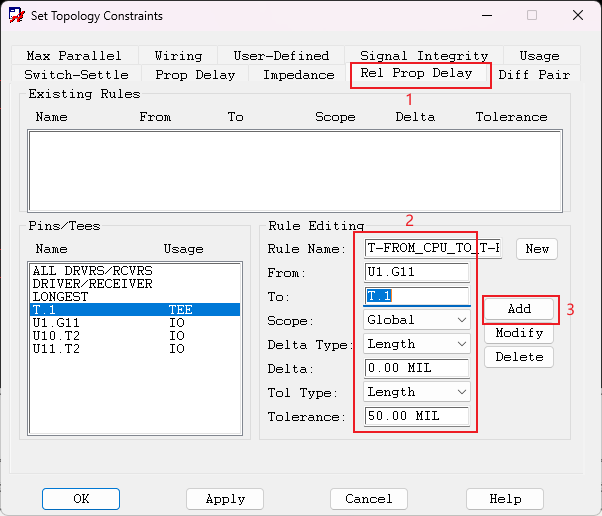

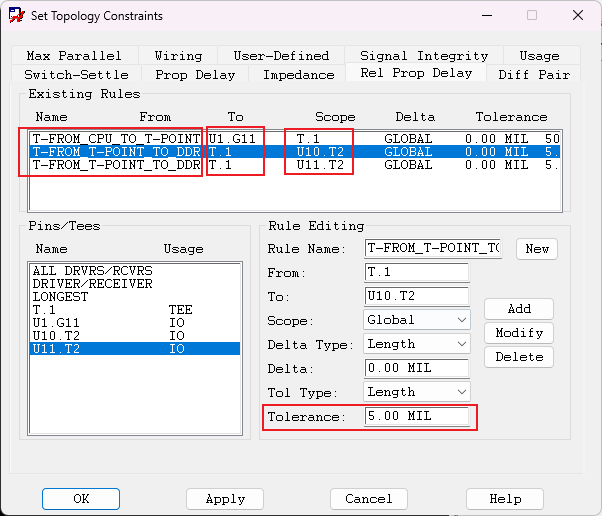

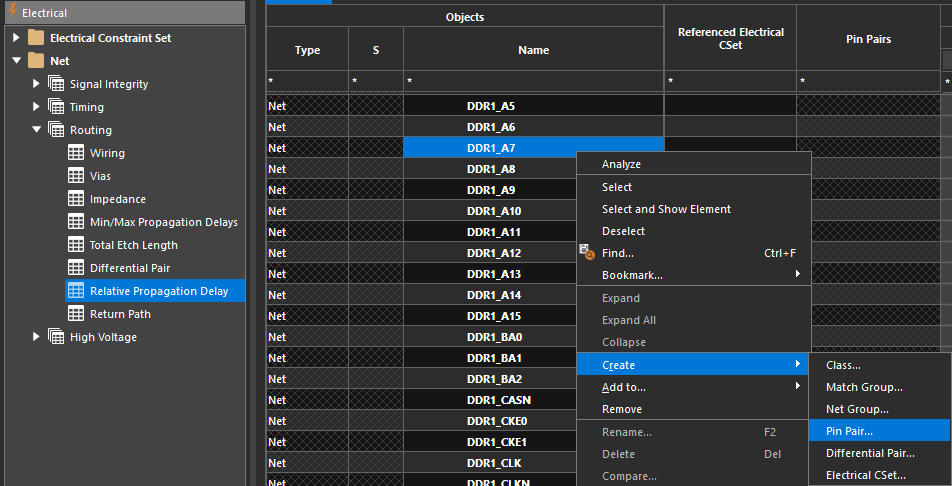

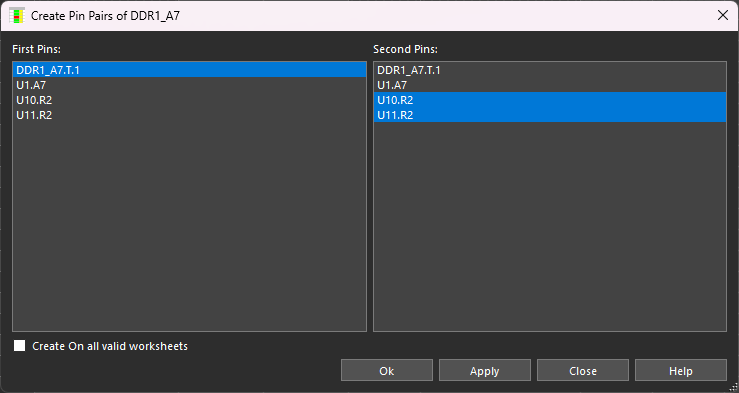

(6)设置等长规则

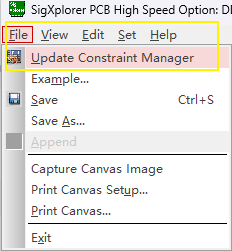

设置T点后得保存,否则这个不行。

这是完成了一个,用这个批量生成:

14分的时候根据RK的手册得出长度误差,没看懂。

左右两端的 Rule Name 可以是一样的:

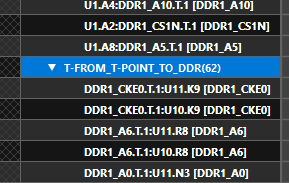

T-FROM_CPU_TO_T-POINT

T-FROM_T-POINT_TO_DDR

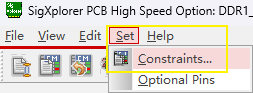

点击OK,然后:

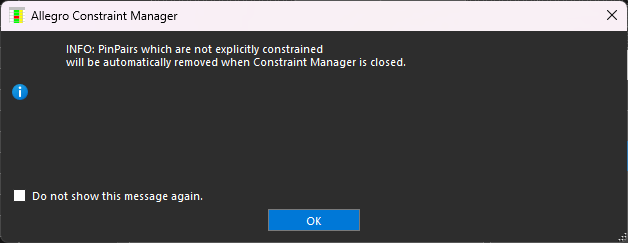

弹出一个界面,点击确认,然后就可以关闭这个页面了。

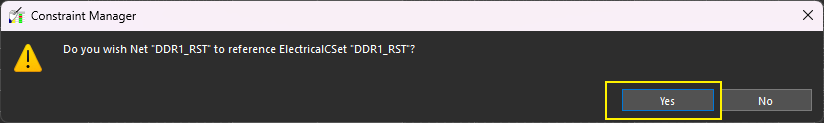

关闭后会弹出,点击Yes:

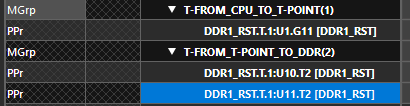

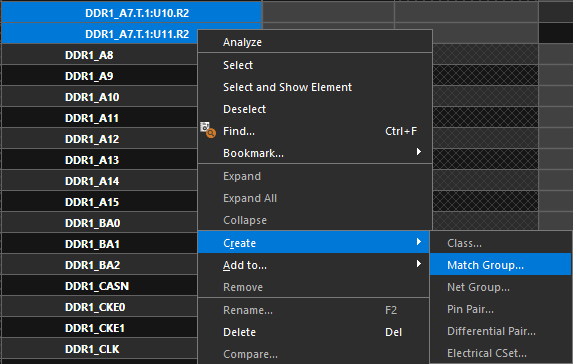

最终会生成两个等长组,和一个规则:

此时给DDR地址组设置 CSet

它就会把所有等长组建立好:

如果说中间的没有连接在CPU上,那必须把 T 点手动放在中间的过孔上,此时Allegro计算的是到T点的长度,而不是到过孔的长度。

但是如果中间的连接在CPU上了,T点无论位置放哪,其实是没有影响的。

2、移动的时候捕捉到过孔上:

3、等长最难做的是中间的,因为线比较短,而且没啥空间。

4、如果线短,先在顶层尽可能拉到最长,减小内层的走线压力,然后再内层。

5、中间实在没地方了,没办法了,就2倍间距。很多时候只能手动拉蛇形

6、时钟线距离其它线最好是4W以上,最小3W

没啥技巧,调整线的时候,中间的留点空间。

这个T点有点毛病,就是某个网络连接好线后,他就不显示T点的飞线了,T点上也没有网络名,不知道哪个是哪个。

还好移动的时候,下面显示网络名称:

如果是使用简单的方案,反而设置比较麻烦:

(1)地址组等长

(2)每个信号创建T点

(3)每个信号的分支创建等长组

然后就是设置 Target 和误差范围了。