PCB 的结构

层叠:多层板是由多种不同的介质(PP片 + CORE芯板)压合而成的

半固化片,又称预浸材料,是用树脂浸渍并固化到中间程度(B 阶)的薄片材料。半固化片可用作多层印制板的内层导电图形的黏结材料和层间绝缘。在层压时,半固化片的环氧树脂融化、流动、凝固, 将各层电路毅合在一起,并形成可靠的绝缘层。

芯板是一种硬质的、有特定厚度的、两面包铜的板材,是构成印制板的基础材料。通常我们 所说的多层板是由芯板和半固化片互相层叠压合而成的。而半固化片构成所谓的浸润层,起到粘合芯板的作用,虽然也有一定的初始厚度,但是 在压制过程中其厚度会发生一些变化。

简言之,芯板就是 PCB 板的总体支撑,半固化片就是隔绝层与层之间的铜皮的。

PCB 层叠设计

二层板

最简单,只有一种方案:

Top-Bottom

四层板

四层板有3种方案:

Top-Gnd02-Pwr03-Bottom(常用)

元器件放在 Top 层,最常用的方案。

Top-Pwr02-Gnd03-Bottom

常用于元器件放在 Bottom 层

或者重要信号线在 Bottom 层

Top-Gnd02-Art03-Bottom

关键信号走 Art03 层

Top、Bottom 层覆地铜皮,为 Art03 层屏蔽干扰

六层板

八层板

Top-Gnd02-Sig03-Vcc04-Gnd05-Sig06-Vcc7-Bottom

如何评估需要几层

阻抗计算

对于高速信号线(>100MHz):需要计算阻抗

对于低速信号线:不需要计算阻抗,可以把工艺做大一点,通常线宽和间距 6 ~ 8 mil

常见阻抗匹配信号如下:

50阻抗:WIFI射频信号,DDR2/DDR3地址线、控制线、命令线、DATA线等。

90阻抗:USB差分对。

100阻抗:DDR2/DDR3时钟差分对、DQS差分对、Ethernet收发差分对、HDMI差分对、SATA收发差分对、LVDS差分对以及CSI/DSI差分对等。

阻抗是什么?

为什么要阻抗匹配?

阻抗匹配是一种策略,通过调整传输线的特征阻抗,使其与信号源的输出阻抗、负载阻抗相等。

当阻抗一致时,信号能量可完全传递到负载,避免反射。

阻抗计算的目的是获取走线宽度、走线间距。

阻抗计算是在已知PCB 材质、需要的阻抗(如USB 90欧姆)的情况下,通过修改 线宽、线距 来凑出需要的阻抗。

线宽与阻抗的关系:

间距与阻抗的关系:

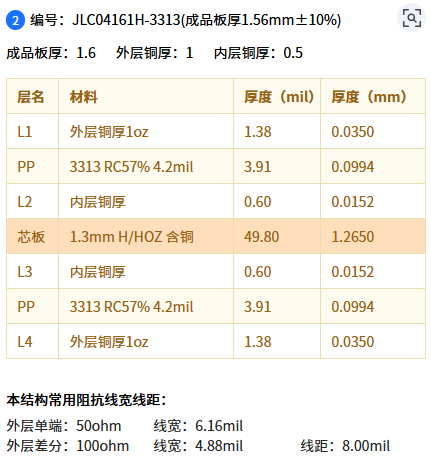

3313、1080、7628 这些是半固化片的类型。

咋没有介电常数。

嘉立创阻抗计算

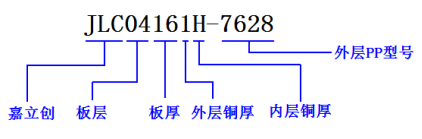

嘉立创阻抗命名规则:

Polar Si9000 阻抗计算

软件下载和安装指导:Polar SI9000 2025 V25.01 阻抗计算神器安装包分享 – 吴川斌的博客

(1)外层特性阻抗模型。(2)内层特性阻抗模型。(3)外层差分阻抗模型。(4)内层差分阻抗模型。(5)共面性阻抗模型。

左侧菜单:

表面微带线:

嵌入式微带线:

Coated Microstrip 1B:

二层板共面阻抗。